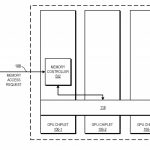

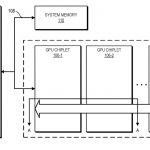

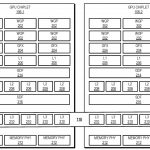

AMD hat am 1. April einen neuen Patentantrag veröffentlicht, der zu zeigen scheint, in welche Richtung sich das Chiplet-GPU-Design entwickelt. Das neue Patent ist eine Weiterentwicklung des vorherigen Patents von AMD, das lediglich eine passive Brücke zwischen den verschiedenen GPU-Chiplets und ihren Verarbeitungsressourcen vorsah.

Das neue Design interpretiert die aktive Brücke, die die Chiplets verbindet, als Last-Level-Cache. Es handelt sich im Wesentlichen um AMDs RDNA 2 Infinity Cache, obwohl er hier nicht nur als Cache verwendet wird (und das mit gutem Effekt, wenn man sich das Infinity Cache Design des RDNA 2 und dessen Leistungssteigerung vor Augen führt); er dient auch als aktive Verbindung zwischen den GPU Chiplets, die den Austausch und die Synchronisation von Informationen ermöglicht, wann und wie auch immer dies erforderlich ist. Dies ermöglicht auch, dass die Registry und der Cache als ein einheitlicher Block für Entwickler offengelegt werden können, wodurch sie entlastet werden, für ein System mit einem Drei-Wege-Cache-Design programmieren zu müssen. Natürlich gibt es auch hier, wie bei AMDs Zen-Chiplet-Designs, Ertragsvorteile und die Möglichkeit, die Leistung zu skalieren, ohne dass monolithische Designs mit hohem Stromverbrauch erforderlich sind. Die integrierte, aktive Cache-Brücke würde sicherlich auch bei der Reduzierung der Latenz und der Aufrechterhaltung der Chiplet Processing Coherency helfen.

Quelle: AMD Patents Chiplet-based GPU Design With Active Cache Bridge