AMD hat bereits bekannt gegeben, dass die CPU-Kernzahl seiner EPYC-Prozessoren „Genua“ und „Bergamo“ 96 bzw. 128 betragen wird. Diese Kernzahl wurde vermutlich durch das größere Glasfasersubstrat des SP5-CPU-Sockels der nächsten Generation ermöglicht, so dass AMD mehr 8-Kern-„Zen 4“-Chiplets, sogenannte CPU Complex Dies (CCDs), einsetzen kann. Bisher hat AMD den Chiplet als gemeinsame Komponente zwischen seinen EPYC Enterprise- und Ryzen Desktop-Prozessoren verwendet, um die Anzahl der CPU-Kerne zu unterscheiden.

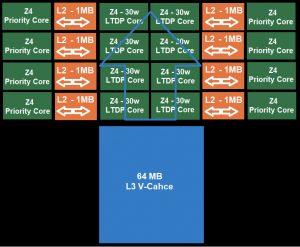

Eine faszinierende Theorie, die in der Gerüchteküche aufgetaucht ist, deutet darauf hin, dass das Unternehmen 5 nm (TSMC N5) nutzen könnte, um größere CCDs mit bis zu 16 „Zen 4“-CPU-Kernen zu entwickeln. Die Hälfte dieser Kerne ist auf ein viel niedrigeres Energiebudget begrenzt, was sie im Wesentlichen zu Effizienz-Kernen macht. Dieses Konzept scheint AMD von seinen mobilen Prozessoren der 15-Watt-Klasse zu übernehmen, bei denen die CPU-Kerne mit einem aggressiven Energiemanagement arbeiten. Diese Kerne liefern immer noch ein vernünftiges Maß an Leistung und sind funktional identisch mit denen von 105-W-Desktop-Prozessoren mit einem entspannten Energiebudget.

Da die „fetten“ und „schlanken“ Kerne funktional identisch sind, muss AMD keine komplexe Middleware wie den Intel Thread Director entwickeln und kann sich mit Optimierungen auf Betriebssystemebene begnügen, die es gemeinsam mit Microsoft oder der Linux-Gemeinschaft entwickeln kann, ähnlich wie bei älteren Versionen der „Zen“-Mikroarchitektur, die mehrere CCXs enthielten.

Die Theorie besagt auch, dass AMD auf der 3D Vertical Cache-Technologie aufbauen könnte. Der CCD der nächsten Generation könnte zwei Schichten aufweisen, die untere Schicht mit CPU-Kernen und ihren dedizierten L2-Caches und eine obere Schicht ausschließlich für einen 64 MB großen 3D Vertical Cache, der als gemeinsamer L3-Cache dient. Beim „Zen 3“-3DV-Cache-CCD befindet sich der 64-MB-SRAM oberhalb des Bereichs des CCD, in dem sich normalerweise der 32-MB-L3-Cache befindet, eine relativ kühlere Komponente als die CPU-Kerne. Beim neuen CCD könnte sich dieses SRAM über dem Bereich mit den Kernen mit niedriger TDP befinden, wodurch die „Leistungs“-Kerne mit hoher TDP an die Peripherie des Chips gedrängt werden, wobei das strukturelle Silizium die Wärme von diesen Kernen an die Oberfläche leitet.

Diese Theorie ist sehr weit hergeholt, aber sie ist plausibel, weil AMD keine beeindruckende Low-Power-CPU-Kernarchitektur hat, die mit „Gracemont“ konkurrieren könnte, und weil Intels „Raptor Lake“-Chips der nächsten Generation Gerüchten zufolge mehr E-Kern-Cluster enthalten werden, was den „i9-13900K“ zu einem Prozessor mit 24 Kernen machen würde, der AMD bei der Kernzahl übertrifft. Wenn wir pingelig sein sollten, würden wir darauf hinweisen, dass die Low-TDP-Kerne genauso viel wertvolle Chipfläche und Transistoranzahl benötigen wie die High-TDP-Kerne; und Chipgröße (d.h. Wafervolumen) ist heutzutage eine ziemlich knappe Ressource. Das werden wir in der zweiten Hälfte des Jahres 2022 herausfinden.