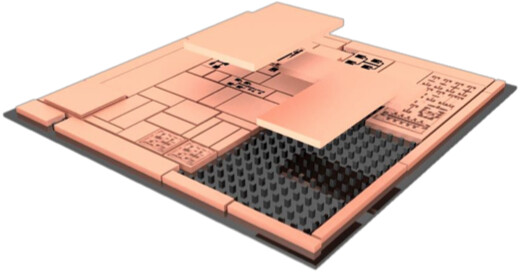

AMD hat ein Patent eingereicht, in dem sie ein MLA-Chiplet-Design beschreiben, das mit einer GPU-Einheit und einer Cache-Einheit gepaart werden kann, um etwas zu schaffen, was AMD ein „APD“ (Accelerated Processing Device) nennt. Das Design würde es AMD ermöglichen, einen Chiplet-basierten Beschleuniger für maschinelles Lernen zu entwickeln, dessen einzige Funktion darin besteht, maschinelles Lernen zu beschleunigen – insbesondere die Matrixmultiplikation. Dies würde Fähigkeiten ermöglichen, die denen von NVIDIAs Tensor-Cores nicht unähnlich sind.

Dies könnte AMD eine modulare Möglichkeit geben, maschinelles Lernen durch die Einbeziehung eines solchen Chips zu mehreren ihrer Designs hinzuzufügen. Dies könnte AMDs Weg sein, eine Hardware-Beschleunigung einer DLSS-ähnlichen Funktion zu erreichen. Außerdem würden die Nachteile vermieden werden, die mit der Implementierung im GPU-Gehäuse selbst verbunden sind: Eine Vergrößerung der Gesamtfläche des Chips und damit höhere Kosten und geringere Erträge. Gleichzeitig ermöglicht diese Technologie AMD sie auch in anderen Produkten als GPU-Gehäusen einzusetzen. Das Patent beschreibt die Möglichkeit, verschiedene Fertigungstechnologien für das Chiplet-basierte Design zu verwenden – in Anlehnung an die I/O-Module in Ryzen-CPUs, die in einem 12-nm-Prozess gefertigt werden und nicht in dem 7-nm-Prozess, der für die Core-Chips verwendet wird. Das Patent beschreibt auch die Beschleunigung von Cache-Anfragen vom GPU-Die an das Cache-Chiplet und dessen sofortige Nutzung als tatsächlichen Cache oder als direkt adressierbaren Speicher.

Quelle: AMD Files Patent for Chiplet Machine Learning Accelerator to be Paired With GPU, Cache Chiplets